## Iraqi Journal for Electrical and Electronic Engineering Original Article

Revised: 27 February 2023

# A Fifteen Levels Inverter with A Lower Number of Devices and Higher Performance

Osama Y. K. Al-Atbee\*, Basim T. Kadhem, Sumer S. Harden, Khalid M. Abdulhassan

Electrical Engineering Department, University of Basrah, Basrah, Iraq

### Correspondence

\*Osama Y. K. Al-Atbee Electrical Engineering Department University of Basrah, Basrah, Iraq. Email: usama.khader@uobasrah.edu.iq

### **Abstract**

Multi-level inverters, as a result of the significant contributions they have made to the fields of high voltage and renewable energy applications, MLI has earned a prestigious place in the field of industrial electronics applications. The use of MLI makes it possible to generate an alternating voltage from a DC voltage or from voltages that are continuously applied thanks to this capability. The quality of the produced wave depends on minimizing the level of total harmonic distortion (THD) in the ensuing output voltage. Increasing the total number of levels is required in order to bring down the THD. The bigger the number of layers, the lower the THD. On the other hand, this necessitates an increase in the number of power switches that are utilized, in addition to an increase in the number of DC sources for certain types. A greater number of levels are achieved in this work with a reduced number of switches, and the DC source necessitates the use of specialized control over the switches as well as the grading of the DC source values. In order to demonstrate that the suggested converter achieves the needed outcomes, the MATLAB simulator is utilized.

KEYWORDS: Inverter, Multi-level inverters, THD reduction, SPWM.

### I. INTRODUCTION

Multilevel inverters are commonly used today because of their voltage operation and functional versatility. The output is generated by a multilayer inverter, which draws power from many DC sources. With an increasing number of DC sources and a constant switching frequency, the inverter's voltage output waveform can be made to seem almost sinusoidal [1]-[4].

The optimal performance of the vast majority of electrical applications can be ensured by utilizing a supply that generates a sinusoidal waveform. The output voltage gets closer to having the shape of a sinusoidal wave as the number of inverter levels gets higher, which results in a decrease in the amount of total harmonic distortion (THD).

The multi-level inverter has a number of advantages over the hard-switched, two-level pulse width modulation (PWM) inverter. These benefits include a decreased dv/dt during high power operations as well as an increase in efficiency [5]-[8].

Three main types of topologies are used for multi-level inverters: cascade, diode clamp, and capacitor clamp. Cascade is the most common topology. The following

topologies are included in this category: The cascade multilevel inverter is the one that requires the least amount of work to put together and has the fewest number of individual parts.

Most of the time, a cascade MLI is built using a series of DC sources and switches that are sequentially connected to one another [9]-[11].

To get the fundamental voltage and get rid of the higherorder harmonics in the output, the switches have to be turned on and off repeatedly so that alternating current voltage can be generated with several levels. This is necessary to accomplish [12].

Several DC sources contribute to its reduced switching losses and stress on the voltage supply. Multilevel inverters continue to be implemented in a growing number of facilities because of their low EMI output, high efficiency, and low switching losses in addition to their high voltage operation capacity.

Multiple levels are represented by the inverter's first three settings [13]. Multilevel inverters are becoming more common in power electronic applications as a result of the higher requirements for power quality and power rating

This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

associated with less harmonic distortion and less electromagnetic interference.

There are a number of benefits to using a multilevel inverter for high switching frequency pulse width modulation (PWM) as opposed to a traditional two-level inverter [14-15].

The following are some of the more appealing aspects of a multilayer inverter:

- Low distortion and dv/dt stress can be used to generate the output voltage.

- The input current has a minimal distortion.

- The common mode voltage is really low.

- It has a low switching frequency.

Power switching devices and capacitor voltage sources are the structural backbone of multilevel inverters.

Due to their capacity to measure output voltage with greater harmonics, high voltages can be achieved with the maximum device rating, making them suited for high-voltage applications and voltage waveforms.

In this paper, a 15-level inverter has been suggested. The suggested multilevel inverter employs fewer switches, is more efficient, and generates fewer losses. Pulse width modulation (PWM) techniques are now widely used due to their low processing requirements, simplicity, and resilience.

The firing pulses for the switching devices are used in a particular PWM technique described in this research to produce a 15-level output voltage. As a reference, one sine waveform source is used in this procedure.

### II. CIRCUIT DESCRIPTION OF PROPOSED 15-LEVEL INVERTER

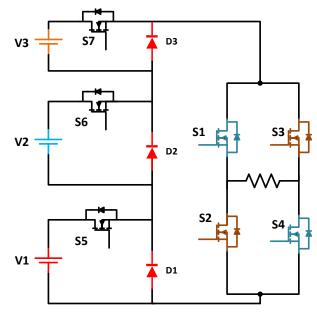

Figure 1 shows the 15-level inverter. The circuit composed of H-Bridge devices with a three DC sources (V1, V2, and V3). Each source connected to the circuit through a switching device (S5, S6, and S7).

In order to understand the operation of the circuit, the operation mode for each output level is describe as following, and since they will be repeated for the remaining modes, just the first seven modes of operation will be detailed for the positive half cycle:

- 1- LEVEL 0 (S1 S4 = ON)

- 2- LEVEL 1 (S1 S4 S5 =ON)

- 3- LEVEL 2 (S1 S4 S6 =ON)

- 4- L3V3L 3 (S1 S4 S5 S6 = ON)

- 5- LEVEL 4 (S1 S4 S7 =ON)

- 6- LEVEL 5 (S1 S4 S5 S7=ON)

- 7- LEVEL 6 (S1 S4 S6 S7 = ON)

- 8- LEVEL 7 (S1 S4 S5 S6 S7 =ON)

- 9- LEVEL 8 (S2 S3 S5 =ON)

- 10- LEVEL 9 (S2 S3 S6 = ON)

- 11- LEVEL 10 (S2 S3 S5 S6 =ON)

- 12- LEVEL 11 (S2 S3 S7 =ON)

- 13- LEVEL 12 (S2 S3 S5 S7 =ON)

- 14- LEVEL 13 (S2 S3 S6 S7 =ON)

- 15- LEVEL 14 (S2 S3 S5 S6 S7=ON)

Fig. 1: The circuit diagram of the 15-level inverter.

### III. THE PROPOSED INVERTER'S SIMULATION MODEL & RESULT

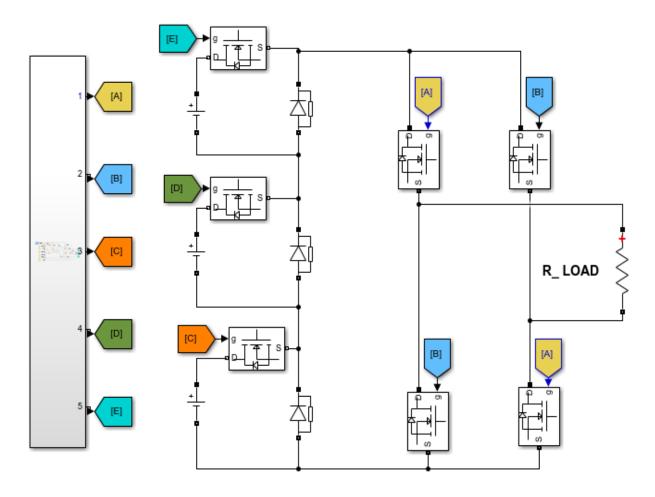

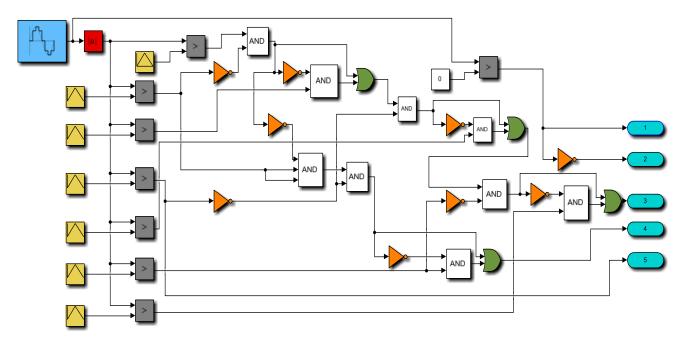

Figure 2 shows the *Matlab-Simulink* model of the proposed inverter, and Fig.3 shows the control circuit of the proposed inverter. Fig.4 shows the timing pulses for the switching devices of the inverter.

This multilevel inverter has three different DC sources to choose from. The voltage that is necessary for each switch can be obtained from its own source. Where, V1=10V, V2=20V, V3=40 V leading to maximum voltage up to 70 Volt. The inverter consists of 3 front end devices (S5-S7) which are connected with a three DC voltage sources.

Using a conventional sinusoidal pulse width modulation, the H-bridge circuit's diagonal switches receive the switching pulses in order to perform their function. When one pair of the diagonal switches is turned on, the other switches are turned off, and vice versa. When S1 and S4 are turned on, the positive half of the waveform is produced, while S2 and S3 produce the negative half of the waveform.

The gate signals for the switches are generated by comparing a 3-phase, (12250 Hz) triangular-carrier signal to a (50 Hz) sinusoidal reference signal in the control circuit. The pulse width modulation approach is used for this.

Fig. 2: The Simulink model of the proposed circuit.

Fig. 3: The control circuit of the 15-level inverter.

Fig. 4: The Timing signals of the control circuit.

The circuit controller is made up of a variety of logical and mathematical MATLAB functions, and it is these functions that are responsible for producing the pulses to control the proposed inverter.

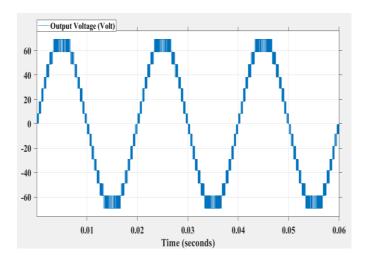

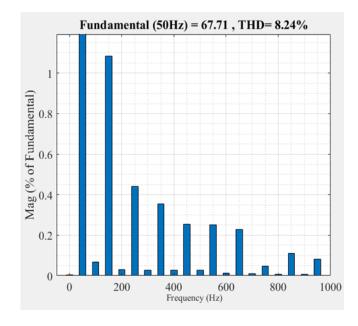

Figure 5 depicts the output voltage of the inverter with 15 levels that has been proposed. Figure 6 illustrates the total harmonic distortion, or THD, that is present in the output voltage. Examining the diagram, one can observe that the THD equal to 8.24 when the modulation index m is about 0.95.

Fig. 5: The 15-level inverter output voltage.

Fig. 6: The total harmonic distortion (THD) of the 15-level inverter.

### IV. CONCLUSION

Multi-level inverters are becoming increasingly significant in today's applications. A 15-level inverter is presented in this work. The proposed inverter may produce a high-quality output voltage while minimizing overall harmonic distortion (THD). In terms of performance, it

outperforms the traditional cascaded multilevel inverter. Using the suggested control strategy, a 15-level output voltage produced with lower THD. The simulation findings show that the new configuration is more effective than the inverters that were previously employed.

#### CONFLICT OF INTEREST

The authors have no conflict of relevant interest to this article.

### REFERENCES

- [1] G. Durga, V. Jegathesan, P. V. V. Rama Rao, "Hybrid multilevel DC link inverter with reduced power electronic switches," 2017 Energy Procedia, Vol. 117, pp.626-634, 2017. doi.org/10.1016/j.egypro.2017.05.162

- [2] A. Prayag and S. Bodkhe, "A comparative analysis of classical three phase multilevel (five level) inverter topologies," 2016 IEEE 1st International Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES), pp. 1-5, 2016. doi: 10.1109/ICPEICES.2016.7853567.

- [3] P. Qashqai, A. Sheikholeslami, H. Vahedi and K. Al-Haddad, "A Review on Multilevel Converter Topologies for Electric Transportation Applications," 2015 IEEE Vehicle Power and Propulsion Conference (VPPC), Montreal, QC, Canada, pp. 1-6, 2015. doi: 10.1109/VPPC.2015.7352882

- [4] A. Kahwa, H. Obara and Y. Fujimoto, "Design of 5-level reduced switches count H-bridge multilevel inverter," 2018 IEEE 15th International Workshop on Advanced Motion Control (AMC), pp. 41-46, 2018. doi: 10.1109/AMC.2019.8371060.

- [5] A. K. Koshti and M. N. Rao, "A brief review on multilevel inverter topologies," 2017 International Conference on Data Management, Analytics and Innovation (ICDMAI), pp. 187-193, 2017. doi: 10.1109/ICDMAI.2017.8073508.

- [6] Balapriyan, P. Veeraragavan, K.," Design and analysis of 7-level inverter at different modulation indices with a closed loop control," International Journal of Pure and Applied Mathematics, pp. 637-641, 2018.

- [7] P. Roseline, B. Ramesh, Ch. V. V. Manga Lakshmi, "Performance Analysis of Twenty Seven Level Asymmetrical Cascaded H-Bridge Multi Level Inverter Fed Three Phase Induction Motor Drive," International Journal of Engineering and Advanced Technology (IJEAT), Vol. 4, Issue 1, October 2014.

- [8] P. Omer, J. Kumar and B. S. Surjan, "A Review on Reduced Switch Count Multilevel Inverter Topologies," in IEEE Access, vol. 8, pp. 22281-22302, 2020. doi: 10.1109/ACCESS.2020.2969551

- [9] J. Rodriguez, Jih-Sheng Lai and Fang Zheng Peng, "Multilevel inverters: a survey of topologies, controls, and applications," in IEEE Transactions on Industrial Electronics, vol. 49, no. 4, pp. 724-738, Aug. 2002. doi: 10.1109/TIE.2002.801052

- [10] Abdulhassan, K. M., Osama Y. K. Al-Atbee. "Improved modified a multi-level inverter with a minimum total

- harmonic distortion." Bulletin of Electrical Engineering and Informatics, Vol. 11.2, pp. 672-680, 2022. doi:10.11591/eei.v11i2.3466.

- [11] Vemula Anil Kumar, and Arounassalame Mouttou, "Improved performance with fractional order control for asymmetrical cascaded H-bridge multilevel inverter." Bulletin of Electrical Engineering and informatics, Vol. 9, no. 4, pp. 1335-1344, 2020.

- [12] Osama Y. K. Al-Atbee, and Khalid M. Abdulhassan. "A cascade multi-level inverter topology with reduced switches and higher efficiency." Bulletin of Electrical Engineering and Informatics, Vol. 12, no. 2, pp. 668-676, 2023. doi.org/10.11591/eei.v12i2.4138.

- [13] M. S. Arif, S. M. Ayob, Z. Salam, "Asymmetrical Nine-Level Inverter Topology with Reduce Power Semiconductor Devices," Telecommunication Computing Electronics and Control, vol. 16, no. 1, pp. 38-45, Feb 2018.

- [14] C. R. Balamurugan, and K. Vijayalakshmi, "Comparative analysis of various z-source based five level cascaded H-bridge multilevel inverter." Bulletin of Electrical Engineering and Informatics, Vol. 7, no. 1, pp. 1-14, 2018.

- [15] C. Dhanamjayulu and S. Meikandasivam, "Implementation and Comparison of Symmetric and Asymmetric Multilevel Inverters for Dynamic Loads," in IEEE Access, vol. 6, pp. 738-746, 2018. doi: 10.1109/ACCESS.2017.2775203